计组-理论-主存储器

存储器概述

1个字节8位,一个字一般2两个或4个字节

性能描述

存取时间:指读或写操作的时间:

- 随机访问存储器:从给定地址到完成读写操作的时间

- 其他类型:将读写机构定位到目标位置所用的时间

存取周期:对于RAM,指两次访问存储单元之间的最小时间间隔

- 第一次访问(读/写)-> 第二次访问(读/写)

带宽:单位时间内存取的数据量

- 一般的随机访问存储器:

- 其他类型:,指读写

N bits所需的平均时间

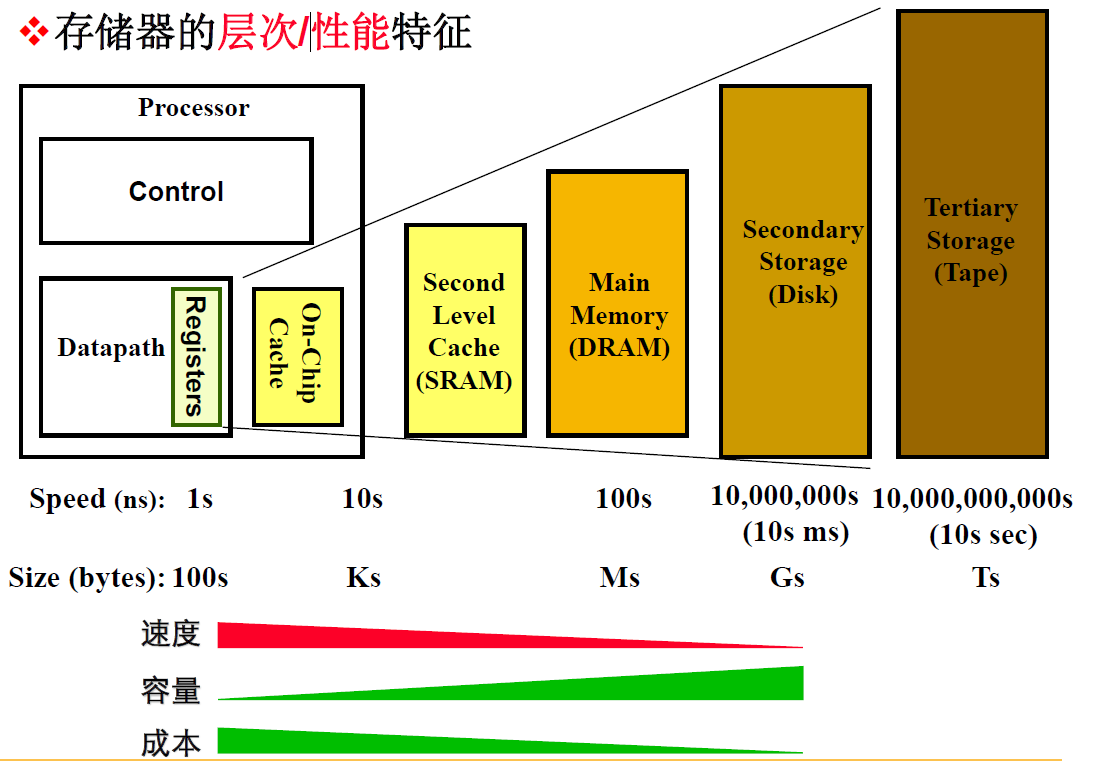

层次描述

分类

半导体存储器从访问方式上区分:

-

RAM:随机存取存储器

- SRAM static:静态:用作Cache

- DRAM dynamic:动态:用作主存

- 静态相对而言集成度低

-

ROM:只读存储器

- 不可在线改写内容的ROM

- 快擦除存储器

存储单元电路

存储单元电路用来存储一位二进制信息。拥有两种稳定状态,来表示二进制的0或1。可以实现状态写入或读出。

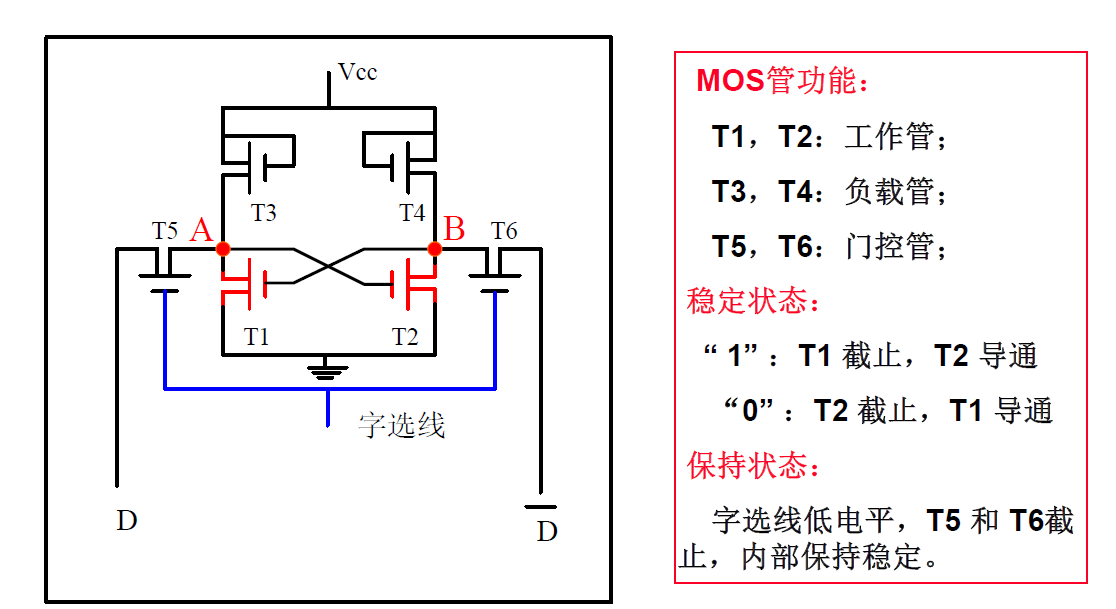

SRAM存储单元电路

- 对于MOS管,当控制端为高电平时,控制MOS管导通。

- 读出操作:

- 输入条件:字选线高电平

- 此时T5和T6导通,如果存储单元原来保存信息是1,则D线则读出A处电平为1,内部状态为1,否则为0。

- 写入操作:

- 写1:D 线高电平,字选线高电平, T5 和 T6 导通, T1 截止,T2 导通,写入 1 。

- 写0:D 线低电平,字选线高电平, T5 和 T6 导通, T2 截止,T1 导通,写入 0 。

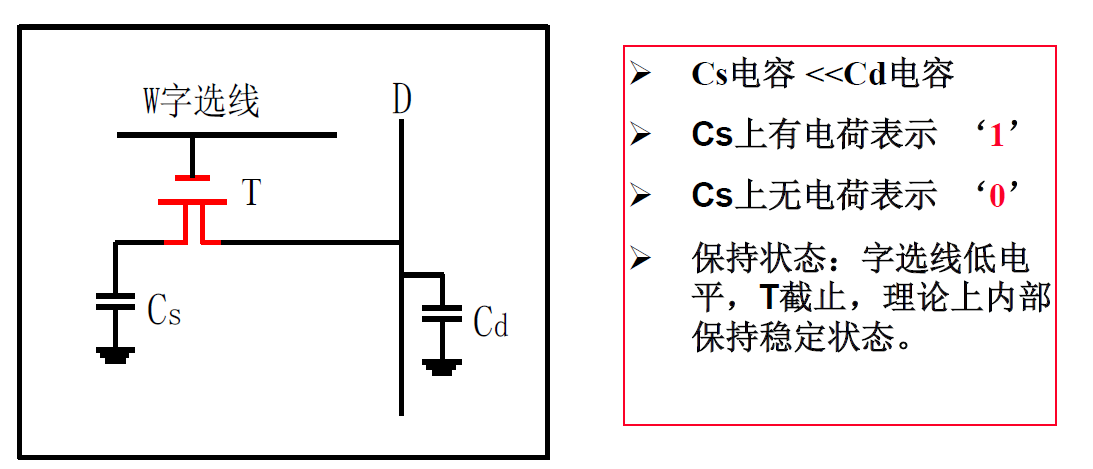

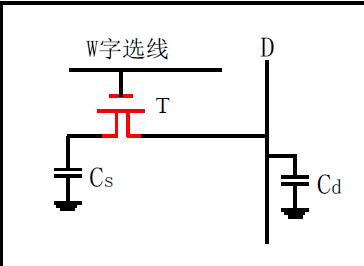

DRAM

刷新:在保存二进制信息“ 1 ”的状态下,Cs有电荷,但Cs存在漏电流,Cs上的电荷会逐渐消失,状态不能长久保持,在电荷泄漏威胁到所保存的数据性质之前,需要补充所泄漏的电荷,以保持数据性质不变。

读出时:根据数据线上电流的方向保存的是1还是0

- D 线先预充电到 Vpre=2.5V,字选线高电平, T 导通

- 若电路保存信息1,Vcs=3.5V电流方向从单元电路内部向外;

- 若电路保存信息0,Vcs=0.0V电流方向从外向单元电路内部;

- 读出过程实际上是 Cs 与 Cd 上的电荷重新分配的过程,也是 Cs 与 Cd 上的电压重新调整的过程。 Cd 上的电压,即是 D 线上的电压。

写入操作:对Cs的充电过程

- D 线加高电平1或低电平0,字选择线置高电平,T 导通;

- 写 1 时, D 线高电平,对 Cs 充电;

- 写 0 时, D 线低电平, Cs 放电;

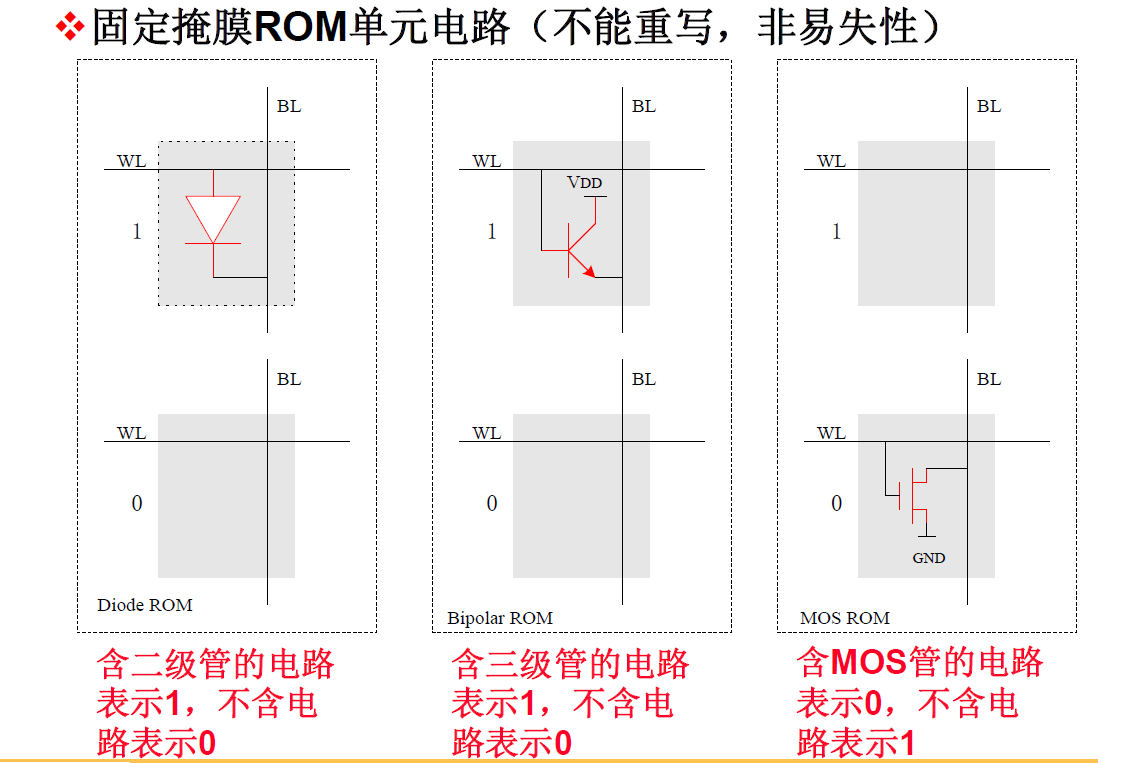

ROM

存储单元电路

存储单元电路的简化表示

存储单元电路(存储位元)→存储芯片→存储器

存储芯片结构

结构

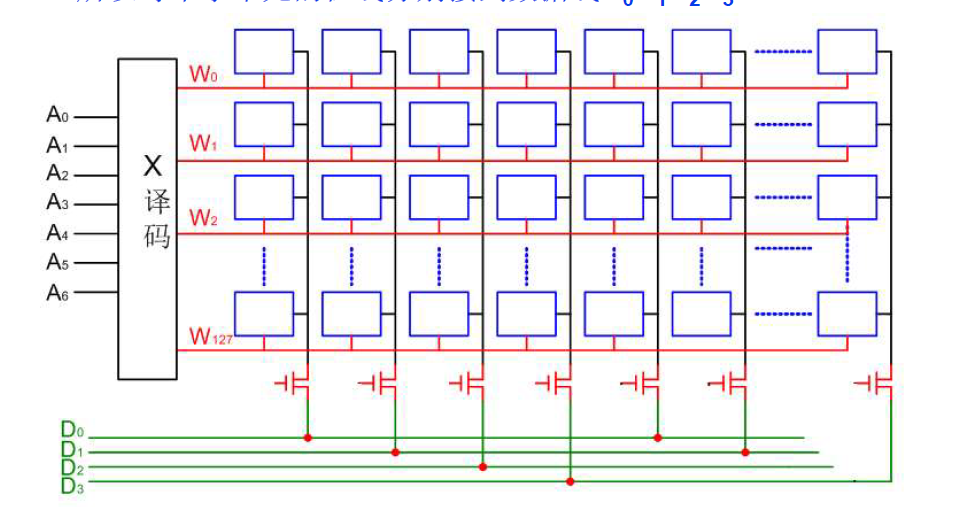

将存储芯片抽象为的形式,即总共有个字,每个字需要m个存储单元

地址线的本质是控制读写的开关,通过译码器实现了对每个存储单元的单独控制。同一个字中的m个存储单元地址相同,由相同的地址线控制读写。每一个字的地址都是唯一的。

对于二维结构,分为行地址和列地址,和一位索引时有所不同,译码器译码后一次打开一行所有存储单元的开关,通过列地址索引实现对值读取的控制:一行中一次只有一个字的读可以导通到数据线D0D1D2D3

对于DRAM,选取行地址数和列地址数相等,但存储单元数不等;对于SRAM,行存储单元数等于列存储单元数

扩展

存储芯片的形式,m、n都有可能不够:

- n不够时将高位的地址作为调控(进制数的性质)

- m不够时将输出信号线接到不同的位上

思路为:

- 同一字空间的芯片CS信号(片选输入管脚)连在一起,高位地址用译码器生成对应的片选信号。

- 同一位空间的数据线连在一起,并连接到对应的数据总线上。

- 根据每个芯片的地址空间范围,设计芯片所需的片选信号逻辑,CS逻辑电路的输入一定是地址总线中,没有连接到芯片地址管脚上的那部分地址线。

DRAM的刷新

为什么刷新

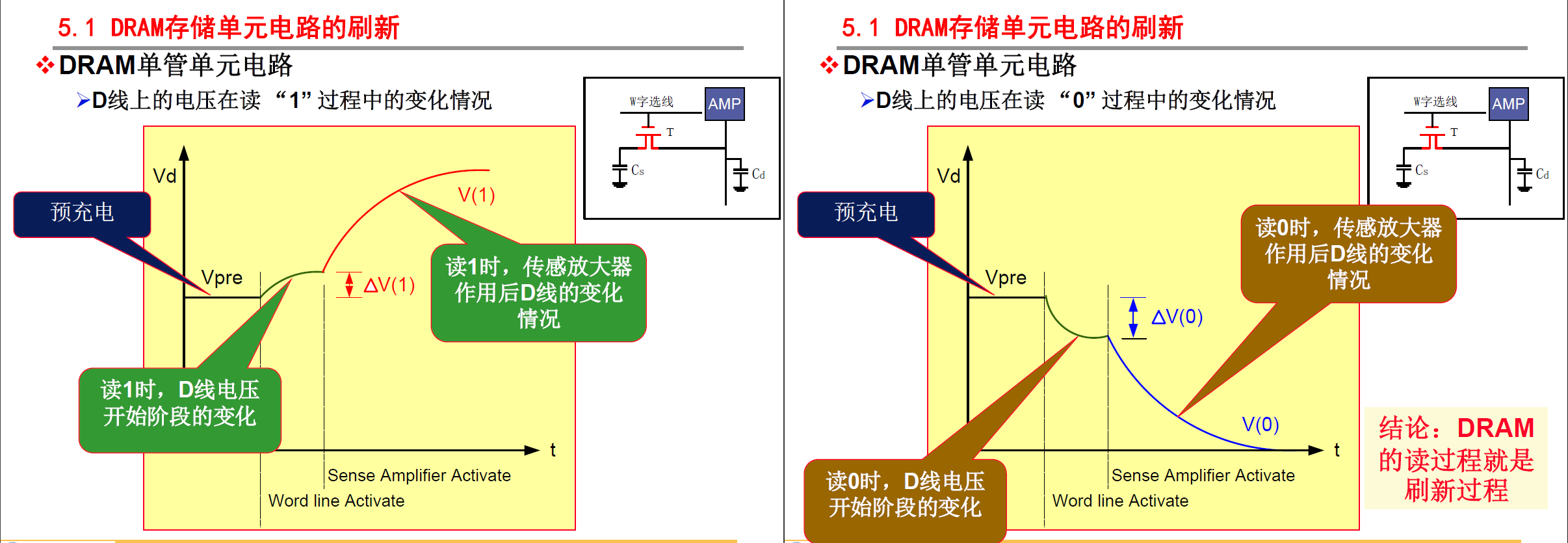

对DRAM的读出操作是一种破坏性操作:读1时,Cs放电;读0时,Cs充电;所以读出操作后,原保存在Cs上的数据(电荷)被破坏,应该立即进行恢复(重写或刷新)。

Cs和Cd两个电容是变脸,Cd>>Cs,对Cs上的电压变化起到了放大效果,在D端能读取到放到后的电压变化,正变化为读出1,负变化为读出0。

尽管Cd有了一定的放大效果,但还是只有100mV左右,太小了,还需要放大

由于读出过程D线电压变化量较小,需要对变化量进行放大,才能得到有效的数据,因此,单管存储单元电路中,D线上必须增加传感放大器(Sense Amplifier)。

- 刷新由传感放大器在读出过程中同时完成。

- 在D线上增加了传感放大器后,读过程实际上就是一次刷新过程。

- 事实上,DRAM的刷新,就是通过这样的读操作来实现的。

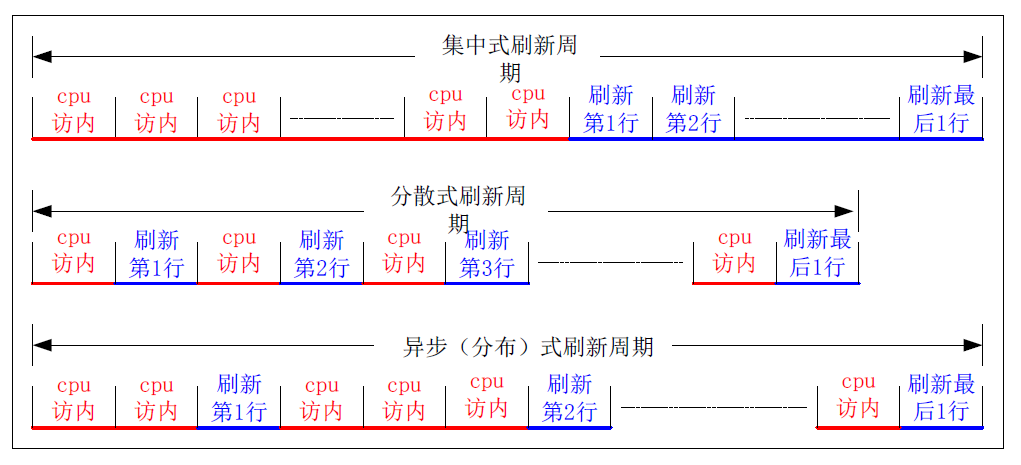

刷新方式

读过程就是一次刷新过程。使用刷新计数器:生成行地址,按行刷新

减少刷新使劲按是渴望的,但是刷新是必需的

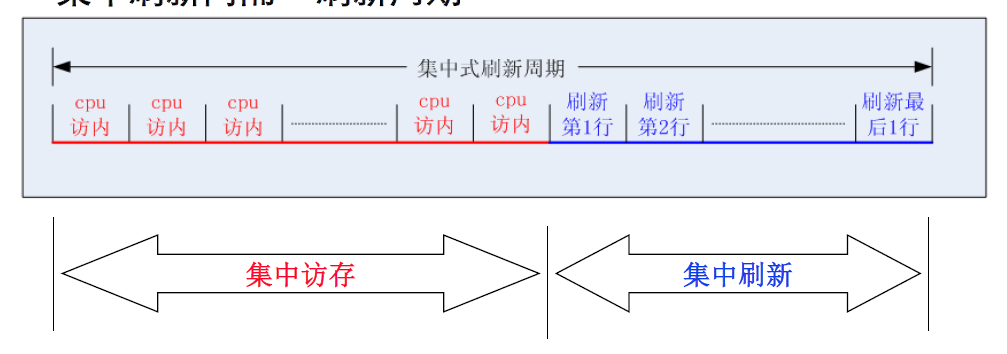

集中刷新方式

将刷新周期分成两部分:在一个时间段内,刷新存储器所有行,此时 CPU 停止访问内存;另一个时间段内,CPU 可以访问内存,刷新电路不工作。

集中刷新间隔= 刷新周期

存在不能进行读写操作的死区时间(刷新时间),很少使用

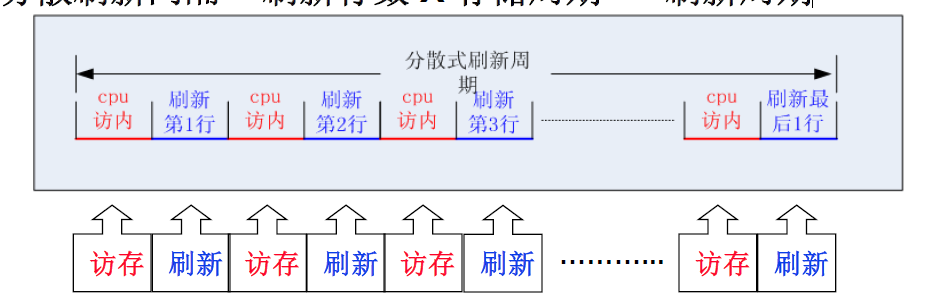

分散刷新方式

CPU与刷新电路交替访问内存,一个存储周期刷新 1 行,下一个存储周期刷新另一行,直至最后 1 行后,又开始刷新第 1 行。

同1行两次被刷新的时间间隔可能小于刷新周期。

分散刷新间隔= 刷新行数 X 存储周期 <= 刷新周期

分散式刷新使系统速度降低,但不存在停止读写操作的死时间

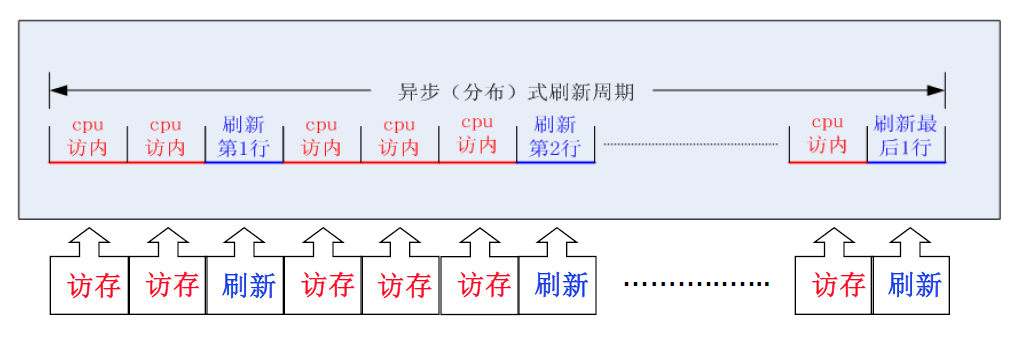

分布式(异步)刷新方式

保证在一个刷新周期内将存储芯片内的所有行刷新一遍,可能等时间间距,也可能不等。

异步刷新间隔= 刷新周期

是前两种方式的结合,可减少死时间,同时保证性能