简要龙芯体系架构

引言

概述

LoongArch为RISC的指令集架构,绝大多数指令只含有两个源操作数和一个目的操作数。

分为32位和64位两个版本。LA64应用级向下兼容LA32:采用LA32 架构的应用软件的二进制可以直接运行在兼容LA64 架构的机器上并获得相同的运行结果,但也只局限于应用软件,系统软件如OS内核不一定可以。

龙芯架构:

- 基础指令

- 非特权指令集:定义了常用的整数和浮点运算

- 特权指令集

- 扩展部分

- 二进制翻译扩展LBT

- 虚拟化扩展LVZ

- 向量扩展LSX

- 高级向量扩展LASX

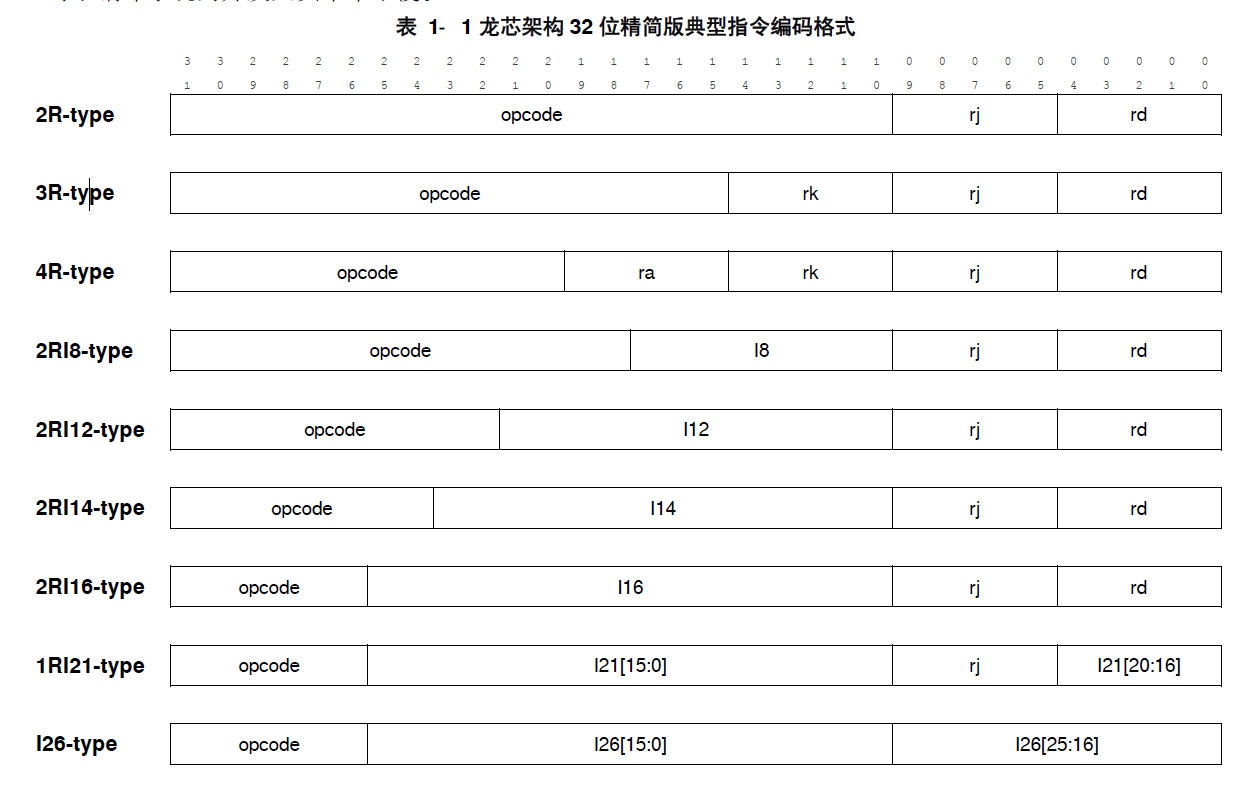

指令编码格式

龙芯架构32位精简版中的所有指令均采用32位固定长度,且指令的地址都要求4字节边界对齐。不对其时发生地址异常。

指令编码的风格是:

- 所有寄存器操作数域都从第0比特开始从低到高依次摆放

- 操作码都是从第31 比特开始从高到低依次摆放。

- 如果指令中包含有立即数操作数,那么立即数域位于寄存器域和操作码域之间,根据不同指令类型有不同的长度。

具体来说,包含9种典型的指令编码格式

- 3种不含立即数的编码格式2R、3R、4R

- 6种含立即数的编码格式2RI8、2RI12、2RI14、2RI16、1RI21、I26

汇编助记格式

特殊区分:

- 通过指令名的前缀字母来区分整数和浮点数指令。所有非向量浮点数指令的指令名以字母“F”开头

- 通过指令名中**“.XX”形式的后缀来指示指令的操作对象**

- 操作对象是整数类型的,指令名后缀为

.B、.H、.W、.BU、.HU、.WU分别表示该指令操作的数据类型是有符号字节、有符号半字、有符号字、无符号字节、无符号半字、无符号字。 - 当操作数是有符号数还是无符号数不影响运算结果时,指令名中携带的后缀均不带U,但此时并不限制操作对象只能是有符号数。

- 对于操作对象是浮点数类型的,或者更具体来说是那些指令名以“F”开头的指令,其指令名后缀为

.H、.S、.D、.W、.WU分别表示该指令操作的数据类型是半精度浮点数、单精度浮点数、双精度浮点数、有符号字、无符号字。

- 操作对象是整数类型的,指令名后缀为

当源操作数和目的操作数数据格式一致时,指令名只有一个后缀。

当不一致时,将有两个后缀,从左到右分别表示目的操作数、源操作数的数据格式。

寄存器操作数用rN代表通用寄存器,用fN代表浮点寄存器。

控制状态寄存器

控制状态寄存器CSR:控制指令的执行行为

每个CSR通常包含若干个域,使用CSR.%%%%.####来代表名为%%%%的控制状态寄存器中的####域

基础整数指令

基础整数格式

数据类型

字长为32位

采用小尾端的存储方式,数据格式采用补码形式

寄存器

基础整数指令涉及的寄存器包括通用寄存器GR和程序计数器PC。

通用寄存器

通用寄存器共有32哥,记为r0~r31,寄存器的位宽为32位

r0寄存器始终为0。

BL指令中的目的寄存器一定是r1:r1固定作为存放函数调用返回地址的寄存器。

PC

PC只有1个,记录着当前指令的地址。

PC 寄存器不能被指令直接修改,它只能被转移指令、例外陷入和例外返回指令间接修改。

特权等级

个运行特权等级PLV,分别是PLV0 和PLV3。

应用软件应运行在PLV3 这个非特权的等级上,与运行在PLV0级上的操作系统等系统软件隔离开。

例外和中断

与MIPS大体相同。较为特殊的是将异常称为例外,中断还是中断。

- 系统调用例外SYS:执行SYSCALL指令将确定地立刻触发系统调用例外

- 断点例外BRK:执行BREAK 指令将确定地立刻触发断点例外

- 指令不存在例外INE:所执行的指令编码在架构中未定义,或者架构规范定义在当前上下文中该指令

视作不存在,那么将立刻触发指令不存在例外 - 特权指令错例外IPE:权限错误:应用软件中执行一条特权指令将确定地立刻触发指令特权等级错例外

- 地址错例外ADEF:当程序有功能错误导致取指出现了非法的情况,即取指地址不是4 字节边界对齐,

此时将触发取指地址错例外

地址空间

按字节寻址

应用软件可使用的地址空间为:

访存形式

分为两种:

-

一致可缓存CC

访问的对象既可以是最终存储对象也可以是处理器中维护有缓存一致性的缓存。

通常采用这种访问类型访问内存以获得高性能。

-

强序非缓存SUC

只能直接访问最终存储对象

==访存类型与虚拟地址绑定,通过页表项中的MAT域决定。==

强序非缓存访问满足顺序一致性:所有访问严格按照程序中的次序执行(==TODO:对于乱序的情况?==),且当前访存操作彻底完成前,不能开始执行下一个访存操作。

Cache一致性维护

某个处理器核的指令Cache与其它处理器核内的Cache或缓存一致输入输出主设备之间的缓存一致性由硬件维护。

处理器核内部指令Cache与数据Cache 之间的缓存一致性维护由软件维护。

- 对于自修改代码,软件需要通过Cache维护指令来保证同一个核内部指令Cache与数据Cache之间的缓存一致性。

- 并且,由于流水线结构和推测取指行为的存在,软件仍需要使用IBAR指令来确保取指一定能够看到store指令的执行效果。

- 在采用软件维护同一核内指令Cache与数据Cache之间的缓存一致性时,code 等于8和9的CACOP指令(即Hit Invalidate I-Cache 和Hit Invalidate and Writeback D-Cache)由特权指令降级为用户态指令。

存储一致性

采用弱一致性WC模型。

在弱一致性模型中,同步操作和普通访存需要区分开来,程序员必须用架构所定义的同步操作把对于写共享单元的访问保护起来,以保证多个处理器核对于写共享单元的访问是互斥的。对访存事件发生次序做如下限制:

同步操作的执行满足顺序一致性条件。

即同步操作在所有处理器核中都严格按照其在程序中出现的次序执行,且在当前同步操作彻底完成之前不能开始执行下一个同步操作。

- 在任一普通访存操作允许被执行之前,所有在同一处理器核中先于这一访存操作的同步操作都已经完成;

- 在任一同步操作允许被执行之前,所有在同一处理机中先于这一同步操作的普通访存操作都已完成。

能够产生同步操作的指令有DBAR、IBAR 以及LL-SC 指令对。

基础整数指令

常规指令略,关注一些特殊指令。

不包含特权指令,特权指令见下一章。

PRELD

访存:preld hint, rj, si12

从内存中预取一个Cache行的数据进入Cache中。

- 访存的地址为rj寄存器内容加上立即数

- hint提示处理器预取的类型以及取回的数据填入哪一Cache,共有32个可选值

- 0:load 预取至一级数据Cache

- 8:store 预取至一级数据Cache

- 其余未定义,当作nop处理

如果访问的Cache表象不是cached,那么该指令不能产生访存动作,视同NOP指令处理。

该指令不会产生异常

原子访存指令

ll.w rd, rj, si14sc.w rd, rj, si14

实现原子的“读-修改-写”访存操作序列

访存操作序列原子性的维护机制是:

- LL.W执行时记录下访问地址并置上标记LLbit为1

- SC.W指令执行时会查看LLbit,仅当LLbit 为1时才真正产生写动作,否则不写。

当软件需要一定成功完成一个原子的“读-修改-写”访存操作序列时,需要构建一个循环来反复执行LL-SC指令对直至SC成功完成。

为了构建这个循环,SC.{W/D}指令会将其执行成功与否的标志(也可以简单理解为SC指令执行时所看到的LLbit 值)写入到通用寄存器rd中返回。

在配对的LL-SC执行期间,下列事件会让LLbit清0:

- 执行了ERTN 指令且执行时CSR.LLBCTL中的KLO 位不等于1;

- 其它处理器核或Cache Coherent I/O master对该LLbit对应的地址所在的Cache行执行完成了一个

store 操作

如果LL-SC指令对访问地址的存储访问属性不是Cached,那么执行结果不确定。

栅障指令

栅障指令(Barrier Instruction)是一种在并行计算中使用的同步机制,用于确保在多线程或多核处理器上执行的多个线程在某个点上达到一致的状态。这种指令通常用于处理线程之间的数据依赖问题,确保在执行后续操作之前,所有线程都完成了之前的操作。

当一个线程执行到栅障指令时,它会等待直到所有其他线程也到达这个点,然后所有线程才会继续执行栅障之后的代码。这可以确保数据的一致性和程序的正确性。

-

dbar hint:用于完成load/store 访存操作之间的栅障功能其携带的立即数hint用于指示该栅障的同步对象和同步程度。hint值为0是默认必须实现的,其指示一个完全功能的同步栅障。

只有等到之前所有load/store访存操作彻底执行完毕后,

DBAR 0指令才能开始执行;且只有DBAR 0执行完成执行后,其后所有load/store访存操作才能开始执行。 -

ibar hint:完成单个处理器核内部store 操作与取指操作之间的同步其携带的立即数hint用于指示该栅障的同步对象和同步程度。hint值为0是默认必须实现的。

它能够确保

IBAR 0指令之后的取指一定能够观察到IBAR 0指令之前所有store 操作的执行效果。

RDCNTV{L/H}.W, RDCNTID

读写时钟Counter中的相应值:

rdcntvl.w rd:读取Counter的[31:0]位写入通用寄存器rd 中rdcntvh.w rd:读取Counter的[63:32]位rdcntid rj:将相应信息写入rj中

基础浮点指令

略

特权资源架构概述

处理器核分为2 个特权等级PLV,分别是PLV0和PLV3。

处理器核当前处于哪个特权等级由CSR.CRMD中PLV域的值唯一确定。

- PLV0 是具有最高权限的特权等级,也是唯一可以使用特权指令并访问所有特权资源的特权等级

- PLV3 这个特权等级不能执行特权指令访问特权资源

特权指令

所有特权指令仅在PLV0 特权等级下才能访问。但是可以在PLV3特权等级下执行Hit类CACOP指令。

CSR访问指令

用于软件访问CSR,所有CSR均为32位。

csrrd rd, csr_num:将指定CSR的值写入到通用寄存器rd中csrwr rd, csr_num:将通用寄存器rd中的旧值写入到指定CSR中,同时将指定CSR的旧值更新到通用寄存器rd中csrxchg rd, rj, csr_num:根据通用寄存器rj中存放的写掩码信息,将通用寄存器rd中的旧值写入到指定CSR中写掩码为1的那些比特,CSR中的其余比特保持不变,同时将该CSR 的旧值更新到通用寄存器rd中。

所有CSR寄存器采用独立的寻址空间。

CSR的寻址单位是一个CSR寄存器,即0号CSR的csr_num是0,1号CSR 的csr_num是1,以此类推。

Cache维护指令

cacop code, rj, si12:主要用于Cache的初始化以及Cache一致性维护

访问的虚拟地址为rj中存储的值加上立即数。

访问哪个Cache以及进行何种Cache操作由指令中5比特的code决定。

code[2:0]指示操作的Cache对象:

- code[2:0]=0表示操作一级私有指令Cache

- code[2:0]=1表示操作一级私有数据Cache

- code[2:0]=2 表示操作二级共享混合Cache。

code[4:3]指示操作类型:

-

code[4:3]=0 表示用于Cache 初始化,将指定Cache行的tag置为全0。

假设被访问的Cache有

1<<Way路,每一路有1<<Index个Cache 行,每个Cache 行大小为1<<Offset个字节,那么采用地址直接索引方式意味着,操作该Cache 的第VA[Way-1:0]路的第VA[Index+Offset-1:Offset]个Cache 行 -

code[4:3]=1表示采用地址直接索引方式维护Cache一致性(Index Invalidate / Invalidate and Writeback)

- 维护一致性的操作是对指定的Cache进行无效并写回的操作。

- 如果被操作的是指令Cache,那么仅需要进行无效操作,并不需要将Cache行中的数据写回。写回的数据进入到哪一级存储中由具体实现的Cache层次及各级间的包含或互斥关系决定。

- 对于数据Cache 或混合Cache,由具体实现决定是否仅在Cache行数据为脏时才将其写回

-

code[4:3]=2表示采用查询索引方式维护Cache 一致性(Hit Invalidate / Invalidate and Writeback)

- 查询索引方式,是将CACOP指令的VA视作一个普通load指令去访问待操作的Cache,如果命中则对命中的Cache 行进行操作,否则不做任何操作

- 查询过程可能涉及虚实地址转换,这种情况下CACOP指令可能触发TLB相关的例外

- 由于CACOP指令操作的对象是Cache行,所以这种情况下并不需要考虑地址对齐与否

-

code[4:3]=3 属于实现自定义的Cache 操作,架构规范中不予明确的功能定义。

TLB维护指令

-

tlbsrch:使用CSR.ASID和CSR.TLBEHI的信息去查询TLB- 如果有命中项,那么将命中项的索引值写入到

CSR.TLBIDX的Index域,同时将CSR.TLBIDX的NE位置为0 - 如果没有命中项,那么将

CSR.TLBIDX的NE位置为1。

- 如果有命中项,那么将命中项的索引值写入到

-

tlbrd:将CSR.TLBIDX的Index域的值作为索引值去读取TLB中的指定项。- 如果指定位置处是一个有效TLB项,那么将该TLB 项的页表信息写入到

CSR.TLBEHI、CSR.TLBELO0、CSR.TLBELO1和CSR.TLBIDX.PS中,且将CSR.TLBIDX的NE位置为0; - 如果指定位置处是一个无效TLB项,需将

CSR.TLBIDX的NE位置为1,且将CSR.ASID.ASID、CSR.TLBEHI、CSR.TLBELO0、CSR.TLBELO1和CSR.TLBIDX.PS全置为0。

- 如果指定位置处是一个有效TLB项,那么将该TLB 项的页表信息写入到

-

tlbwr:将TLB相关CSR中所存放的页表项信息写入到TLB的指定项- 被填入的页表项信息来自于

CSR.TLBEHI、CSR.TLBELO0、CSR.TLBELO1和CSR.TLBIDX.PS - 执行TLBWR 时,页表项写入TLB的位置是由

CSR.TLBIDX的Index域的值指定的。 - 若此时

CSR.ESTAT.Ecode=0x3F,即处于TLB重填例外处理过程中,那么TLB 中总是填入一个有效项(即TLB项的E位为1)。 - 否则的话,就需要看

CSR.TLBIDX.NE位的值。此时如果CSR.TLBIDX.NE=1,那么TLB中会被填入一个无效TLB项;仅当CSR.TLBIDX.NE=0时,TLB 中才会被填入一个有效TLB项。

- 被填入的页表项信息来自于

-

tlbfill:将TLB相关CSR中所存放的页表项信息填入到TLB中- 被填入的页表项信息来自于

CSR.TLBEHI、CSR.TLBELO0、CSR.TLBELO1和CSR.TLBIDX.PS - 执行TLBFILL时,页表项被填入到TLB的哪一项,是由硬件随机选择的。

- 若此时

CSR.ESTAT.Ecode=0x3F,即处于TLB重填例外处理过程中,那么TLB中总是填入一个有效项(即TLB 项的E位为1)。 - 否则的话,就需要看

CSR.TLBIDX.NE位的值。此时如果CSR.TLBIDX.NE=1,那么TLB中会被填入一个无效TLB项;仅当CSR.TLBIDX.NE=0时,TLB中才会被填入一个有效TLB项。

- 被填入的页表项信息来自于

-

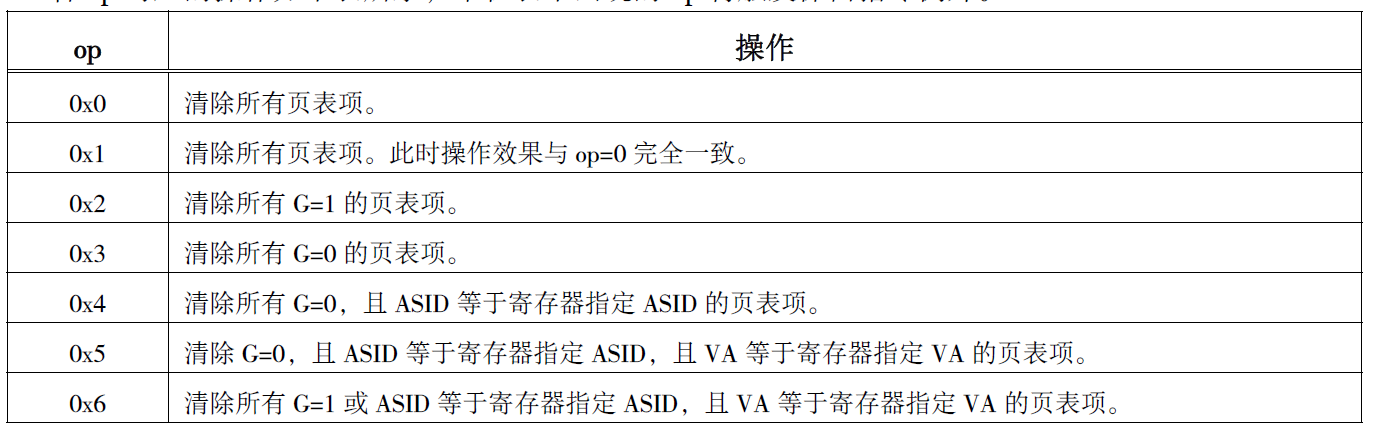

invtlb op, rj, rk:无效TLB中的内容,以维持TLB与内存之间页表数据的一致性。-

rj的[9:0]位存放无效操作所需的ASID信息,其余比特必须填0。当不需要rj时,应设置为r0

-

rk中用于存放无效操作所需的虚拟地址信息。当不需要rk时,应设置为r0

-

op:未在表中出现的op 将触发保留指令例外

-

ERTN

ertn:从例外处理返回

- 将例外对应的PPLV、PIE等信息更新至

CSR.CRMD中,同时跳转到例外所对应的ERA处开始取指。 - 例外对应的PPLV、PIE信息来自

于CSR.PRMD,例外对应的ERA来自于CSR.ERA。

执行ERTN指令时,如果CSR.LLBCTL中的KLO位不等于1,则将LLbit置0,否则LLbit不修改。

IDLE

idle level:IDLE指令执行完毕后,处理器核将停止取指进入等待状态,直至其被中断唤醒或被复位。从停止状态被中断唤醒后,处理器核执行的第一条指令是IDLE 之后的那一条指令。

存储管理

内存物理地址空间范围是:。

PALEN理论上是一个不超过36的正整数,由实现决定其具体的值,通常为32。

地址映射

MMU支持两种虚实地址翻译模式:直接地址翻译模式和映射地址翻译模式。

-

当

CSR.CRMD的DA=1且PG=0时,处理器核的MMU处于直接地址翻译模式。物理地址默认直接等于虚拟地址的

[PALEN-1:0]位(不足补0),除非具体实现中采用了其它优先级更高的虚实地址翻译规则。 -

当

CSR.CRMD的DA=0且PG=1时,处理器核的MMU处于映射地址翻译模式。具体又分为直接映射地址翻译模式和页表映射地址翻译模式两种。

翻译地址时将优先看其能否按照直接映射模式进行翻译,无法进行后再按照页表映射模式进行翻译。

直接翻译模式:直接映射配置窗口共设置有两个,可同时用于取指和load/store操作。

- 系统软件通过配置

CSR.DMW0~CSR.DMW1寄存器来分别设置两个直接映射配置窗口。每个窗口除了地址范围信息外,还可以配置该窗口在哪些特权等级下可用,以及虚地址落在该窗口上的访存操作的存储访问类型。 - 每一个直接映射配置窗口可以配置一个字节固定大小的虚拟地址空间。当虚地址命中某个有效的直接映射配置窗口时,其物理地址直接等于虚地址的[28:0]位拼接上该映射窗口所配置的物理地址高位。

- 命中的判断方式是:虚地址的最高3位。即[31:29]位,与配置窗口寄存器中的[31:29]相等,且当前特权等级在该配置窗口中被允许。

存储访问类型

支持两种存储访问类型,分别是:一致可缓存CC和强序非缓存SUC。

-

当处理器核MMU处于直接地址翻译模式时,所有取指的存储访问类型由

CSR.CRMD.DATF决定,所有load/store操作的存储访问类型由CSR.CRMD.DATM域决定。 -

当处理器核MMU 处于映射地址翻译模式时,存储访问类型的确定分为两种情况,其存储访问类型由页表项中的MAT域决定。

-

0:强序非缓存

-

1:一致可缓存

-

2/3:保留

-

页表映射存储管理

映射地址翻译模式下,除了落在直接映射配置窗口中的地址之外,其余所有合法地址都必须通过页表映射完成虚实地址转换。

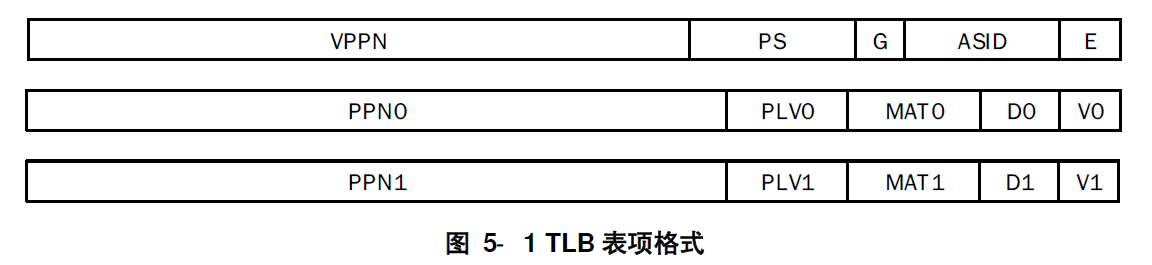

TLB的规格

TLB 采用全相联查找表的组织形式。

每一个TLB 表项包含两个部分:比较部分和物理转换部分。

比较部分:

| 位 | 长度/bit | 作用 |

|---|---|---|

| 存在位E | 1 | 为1表示所在TLB 表项非空,可以参与查找匹配 |

| 地址空间标识ASID | 10 | 用于区分不同进程中的同样的虚地址,避免进程切换时清空整个TLB 所带来的性能损失 |

| 全局标志位G | 1 | 当该位为1时,查找时不进行ASID是否一致性的检查。 当操作系统需要在所有进程间共享同一虚拟地址时,可以设置TLB页表项中的G位置为1 |

| 页大小PS | 6 | 仅在MTLB 中出现。用于指定该页表项中存放的页大小。数值是页大小的2的幂指数。 龙芯架构32 位精简版只支持4KB和4M 两种页大小 |

| 虚双页号VPPN | VALEN-13 | 在龙芯架构32 位精简版中,每一个页表项存放了相邻的一对奇偶相邻页表信息,故即虚页号的最低位不需要存放在TLB 中。 查找TLB 时在根据被查找虚页号的最低位决定是选择奇数号页还是偶数号页的物理转换信息。 |

物理转换部分:

| 位 | 长度/bit | 作用 |

|---|---|---|

| 有效位V | 1 | 为1表明该页表项是有效的且被访问过的 |

| 脏位D | 1 | 为1表示该页表项所对应的地址范围内已有脏数据 |

| 存储访问类型MAT | 2 | 控制落在该页表项所在地址空间上访存操作的存储访问类型 |

| 特权等级PLV | 2 | 该页表项对应的特权等级。该页表项可以被任何特权等级不低于PLV的程序访问 |

| 物理页号PPN | VALEN-12 | 当页大小大于4KB的时候,TLB中所存放的PPN 的[PS-1:12]位可以是任意值。 |

基于TLB的地址转换过程

1 | # va: 待查找虚地址 |

TLB相关的异常

略,见手册

异常与中断

中断

中断基本情况

中断采用线中断的形式。每个处理器核内部可记录12 个线中断,分别是:

- 1个核间中断IPI

- 1 个定时器中断TI

- 8 个硬中断HWI0~HWI7

- 2 个软中断SWI0~SWI1

所有的线中断都是电平中断,且都是高电平有效。

核间中断的中断输入来自于核外的中断控制器,其被处理器核采样记录在CSR.ESTAT.IS[12]位。

- 定时器中断的中断源来自于核内的恒定频率定时器。当恒定频率定时器倒计时至全0值时,该中断被

置起。置起后的定时器中断被处理器核采样记录在CSR.ESTAT.IS[11]位。清除定时器中断需要通过软件向

CSR.TICLR 寄存器的TI 位写1 来完成。 - 硬中断的中断源来自于处理器核外部,其直接来源通常是核外的中断控制器。8个硬中断

HWI[7:0]被处

理器核采样记录在CSR.ESTAT.IS[9:2]位。 - 软中断的中断源来自于处理器核内部,软件通过CSR指令对

CSR.ESTAT.IS[1:0]写1则置起软中断,写

0则清除软中断。

中断在CSR.ESTAT.IS 域中记录的位置的索引值也被称为中断号。SWI0 的中断号等于0,SWI1 的中断号等于1,IPI 的中断号等于12。中断号越大优先级越高。

中断处理过程

各中断源发来的中断信号被处理器采样至CSR.ESTAT.IS域中,这些信息与软件配置在CSR.ECFG.LIE域中的局部中断使能信息按位与,得到一个多位中断向量int_vec。

当CSR.CRMD.IE=1且int_vec不为全0时,处理器认为有需要响应的中断,于是从执行的指令流中挑选出一条指令,将其标记上一种特殊的例外——中断例外。

例外

其实就是异常。

例外入口

TLB 重填例外的入口来自于CSR.TLBRENTRY

除上述例外之外的所有普通例外入口相同,来自于CSR.EENTRY。此时需要软件通过CSR.ESTA 中的Ecode、IS 域的信息来判断具体的例外类型。

例外优先级

-

中断的优先级高于例外

-

对于例外:

-

取指阶段检测出的优先级最高

- 取指地址错例外优先级最高

- 取指TLB 相关例外优先级次之

-

译码阶段检测出的优先级次之

可检测出的例外彼此互斥,故无需考虑其间的优先级

-

执行阶段检测出的优先级再次之

仅访存指令或同时触发多种例外:要求地址对齐的访存指令因地址不对齐而产生的地址对齐错例外ALE > TLB相关的例外

-

例外处理过程

当触发例外时,处理器硬件会进行如下操作:

- 将

CSR.CRMD的PLV、IE分别存到CSR.PRMD的PPLV、PIE中,然后将CSR.CRMD的PLV置为0,IE置为0; - 将触发例外指令的PC值记录到

CSR.ERA中; - 跳转到例外入口处取指。

当软件执行ERTN 指令从例外执行返回时,处理器硬件会完成如下操作:

- 将

CSR.PRMD中的PPLV、PIE值恢复到CSR.CRMD的PLV、IE中 - 跳转到CSR.ERA 所记录的地址处取指。

复位

复位将重新处理器核中的所有逻辑,将电路置于确定的状态。

复位后第一条指令的PC是0x1C000000。由于复位撤销后MMU一定处于直接地址翻译模式,所以复位后所取的第一条指令的物理地址也是0x1C000000。

复位撤销后,处于确定状态的寄存器内容有:

CSR.CRMD的PLV=0,IE=0,DA=1,PG=0,DATF=0,DATM=0;CSR.EUEN的FPUen为0;CSR.ECFG中的LIE 为0;CSR.ESTAT中IS[1:0]均为0;CSR.TCFG的En=0;CSR.LLBCTL的KLO=0;- 所有实现的

CSR.DMW中的PLV0、PLV3 均为0;

除了上述指定的内容外,复位撤销后,处理器中其它软件可见的寄存器的值都是不确定的,软件在使用前都要将其状态置于确定状态。

TLB 和Cache 在复位期间是否进行硬件复位由实现决定,若未实现则需要进行软件复位。

控制状态寄存器

见手册